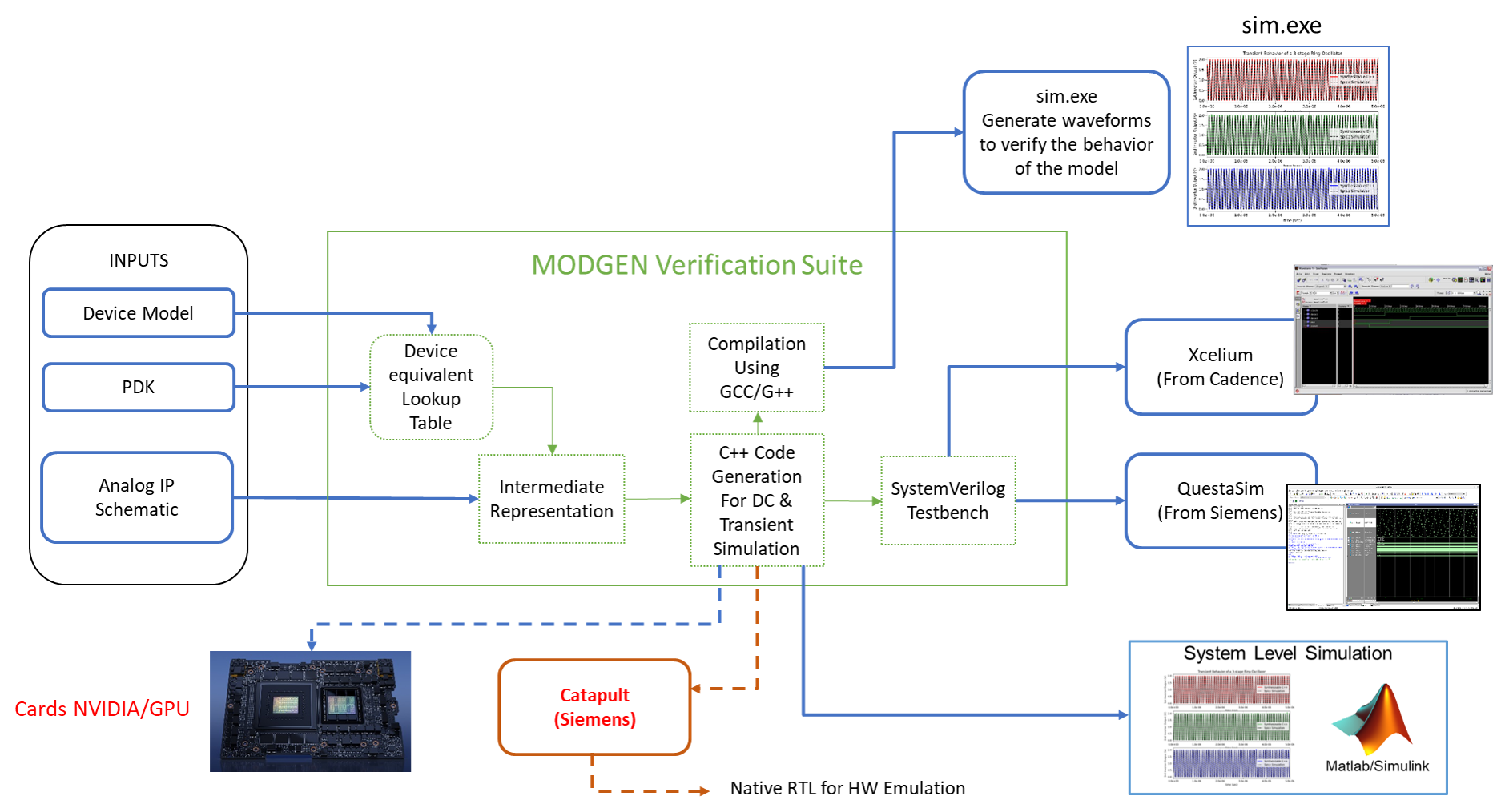

MODGEN Project: Automatic Generation of Spice-Accurate Real Number Models for Fast Analog and Mixed Signal Verification

Figure 1: MODGEN System Architecture

MOGEN Project Objectives:

The main objective of the MODGEN project is to automate the generation of human-readable, synthesizable, simulatable, debuggable and spice-accurate real number models (RNM) to alleviate the burden of analog and mixed signal verification during System-on-Chip Verification. These real number models are fully integrated in system level simulation environments and are debuggable using analog mixed-signal debuggers. They can be compiled as standalone C++ code and executed to generate all the waveforms in an AMS circuit. These RN models can be synthesized as native RTL or bitstreams for FPGA. In addition, they can be deployed on NVIDIA GPUs to accelerate Spice simulation. Worthmentioning that the generated models captures all circuit nonidealities in a seamless manner.

Expected Results:

Today, we target simulation speed-up from 10x to 1000x.

Actual Target Circuit:

We look to model a complete Phase-Locked Loops (PLL) and measure the speedup in simulation and verification times.